# 11 V Boosted Mono Class D Amplifier with DSP

| Speaker Amplifier Features                                          | System Protection Features                                                           |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Class D architecture with adaptive output stage reduces             | IC thermal self-protection against overtemperature                                   |

| idle power consumption and switching losses                         | <ul> <li>System supply rail reactive brownout system protection</li> </ul>           |

| Digital input supports I <sup>2</sup> S or TDM serial audio         | <ul> <li>Speaker current sensing via integrated</li> </ul>                           |

| <ul> <li>5.3 W @ 1% THD+N into 8 Ω (1 kHz, VP = 4.3 V)</li> </ul>   | current-monitoring sense resistor                                                    |

| <ul> <li>6.0 W @ 10% THD+N into 8 Ω (1 kHz, VP = 4.3 V)</li> </ul>  | <ul> <li>Current and voltage monitor data on I<sup>2</sup>S/TDM interface</li> </ul> |

| <ul> <li>Shared boost rail supply option</li> </ul>                 | DC input watchdog                                                                    |

| <ul> <li>11 V amplifier supply maximum voltage</li> </ul>           |                                                                                      |

| <ul> <li>Programmable digital volume and amplifier gain</li> </ul>  | Digital Boost Converter Features                                                     |

| <ul> <li>Low idle channel noise: 9 µVrms (A-weighted)</li> </ul>    | <ul> <li>Class H envelope-tracking boost supply</li> </ul>                           |

| <ul> <li>–78 dB THD+N @ 1 W into 8 Ω (1 kHz, VP = 3.6 V)</li> </ul> | <ul> <li>Integrated boost and rectification FETs</li> </ul>                          |

| <ul> <li>Advanced ΔΣ closed-loop architecture</li> </ul>            | <ul> <li>High-bandwidth digital control loop</li> </ul>                              |

| <ul> <li>Amplifier short-circuit protection</li> </ul>              | 2 MHz switching frequency                                                            |

| Multidevice synchronization                                         | <ul> <li>Synchronous rectification in Boost Active Mode</li> </ul>                   |

|                                                                     | Pulse-skipping mode for improved efficiency during low                               |

| Configuration and Diagnostic Features                               | power quiescent operation                                                            |

| Diagnostic signal generator for rapid test development              | <ul> <li>Programmable boost voltages of up to 11 V</li> </ul>                        |

| <ul> <li>Soft reset via I<sup>2</sup>C/SPI control port</li> </ul>  |                                                                                      |

| Hardware reset via pin                                              |                                                                                      |

| ·                                                                   |                                                                                      |

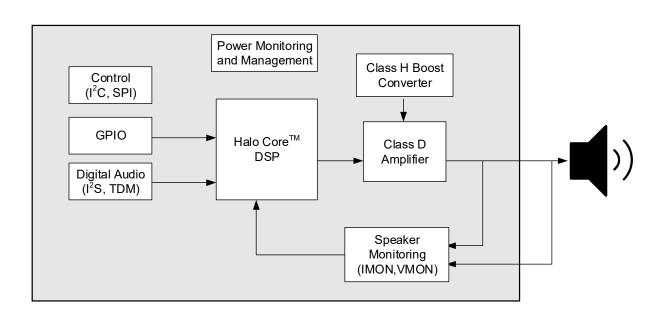

#### **General Description**

The CS35L42 integrates a high-performance mono audio amplifier, 130 MCPS Halo Core<sup>TM</sup> DSP, and amplifier voltage boost converter to enable an easy-to-integrate speaker playback solution performing both robust transducer protection and enhancement functions.

The integrated DSP performs all required audio path equalization, enhancement, and protection while off-loading the application processor, allowing an overall lower system power state during audio playback. PLL-based internal clock generation from the audio serial timing supports a range of sample rate options from 44.1–96 kHz without an additional external MCLK reference clock source, further easing system integration.

The Class D amplifier features an advanced closed-loop architecture providing superior power supply rejection ratio (PSRR), and a complementary output stage. The elevated VBST supply generated by the boost converter allows the CS35L42 to deliver up to 5.3 W into an 8  $\Omega$  speaker and 5.5 W into a 6  $\Omega$  speaker at 1% THD+N.

The digitally controlled boost converter boosts standard-voltage lithium-ion and lithium-polymer battery voltages up to 11 V. The boost converter's output voltage automatically tracks the audio using an integrated Class H algorithm or can be configured via software control interface. A configurable weak-drive mode allows automatic reduction of power consumption during idle (low-output power) conditions by reducing switching losses.

The enhancement algorithms are designed to provide flexible tuning capability for a high performance portable audio system. Speaker protection algorithms are complete and robust, requiring minimal parameter settings to configure for the specific speaker and the associated speaker back volume and acoustics. Cirrus Logic provides an optimized tool chain to facilitate creating and programming the appropriate coefficients for enhancement and speaker protection for development and mass production. Cirrus Logic also provides Android device drivers for the CS35L42.

The CS35L42 includes self-protection and system-protection features as well. The boost and amplifier stage are protected against short circuits. IC overtemperature shutdown protection is provided in hardware.

The supply voltage is continuously monitored. The boost converter and amplifier gain are automatically adjusted to preserve the supply voltage according to programmable voltage/current load-shedding setpoints. The supply voltage protection adjustment of the amplifier is integrated with the IC and speaker thermal protection, ensuring seamless coordination of gain rollback.

Multidevice synchronization enables parameters such as gain levels to be cross-communicated with other Cirrus Logic audio and haptics amplifiers in the same system, maintaining stereo image balance and total system current budget.

The CS35L42 is available in a commercial-grade 0.4-mm pitch, 30-ball wafer level chip scale package for operation from -40° to +85°C. See Section 12 for ordering information.

# **1** Pin Descriptions

These sections show pin assignments and describe pin functions.

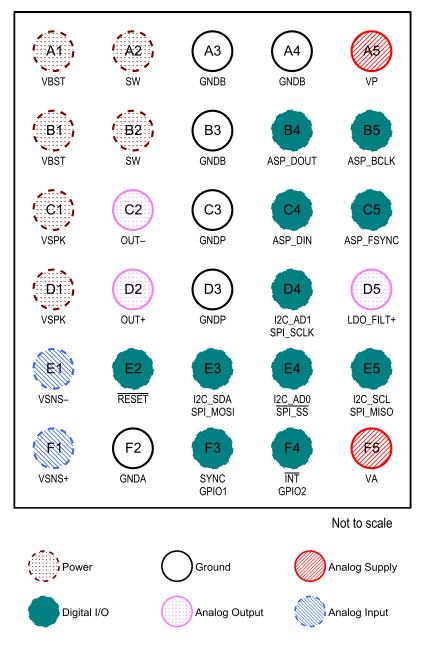

# 1.1 WLCSP Package Drawing (Top View, Through Package)

Figure 1-1. WLCSP 30-Ball Package Assignments (Top View, Through-Package)

# 1.2 Pin Descriptions

#### Table 1-1. WLCSP Pin Descriptions

| Pin Name             | Ball #                                                                                                            | Power<br>Supply | I/O               | Description                                                                                                                                                                                                                                              | Internal<br>Connection | State at<br>Reset |

|----------------------|-------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------|

| ASP_BCLK             | BCLK         B5         VA         I/O         Audio Serial Port Bit Clock. Serial shift clock for the interface. |                 | Weak<br>pull-down | Weak<br>pull-down                                                                                                                                                                                                                                        |                        |                   |

| ASP_DIN              | C4                                                                                                                | VA              | I/O               | Audio Serial Port Data Input. I2S and TDM serial audio input.                                                                                                                                                                                            | Weak<br>pull-down      | Weak<br>pull-down |

| ASP_DOUT             | B4                                                                                                                | VA              | 0                 | Audio Serial Port Data Output. I <sup>2</sup> S and TDM serial audio data output.                                                                                                                                                                        | Weak<br>pull-down      | Weak<br>pull-down |

| ASP_FSYNC            | C5                                                                                                                | VA              | I/O               | Audio Serial Port Frame Sync Clock. Identifies the start of<br>each serialized PCM data word and indicates which channel, left<br>or right, is active on the serial PCM audio data lines or indicates<br>the start of each TDM frame.                    | Weak<br>pull-down      | Weak<br>pull-down |

| GNDA                 | F2                                                                                                                | _               | _                 | <b>Analog and Digital Ground.</b> Ground reference for the analog and digital portions of the IC.                                                                                                                                                        | _                      | _                 |

| GNDB                 | A3, A4,<br>B3                                                                                                     | —               | _                 | <b>Boost Converter Ground.</b> Ground reference for the internal boost converter.                                                                                                                                                                        | _                      | —                 |

| GNDP                 | C3, D3                                                                                                            |                 |                   | <b>Power Ground.</b> Ground reference for the boost converter and Class D amplifier's output stage.                                                                                                                                                      | —                      | _                 |

| I2C_AD0/SPI_SS       | E4                                                                                                                | VA              | I                 | I <sup>2</sup> C Slave Device Address Select 0. Used with I2C_AD1,<br>connected to VA or GNDA, to select between four possible<br>addresses.<br>SPI Control-Port Slave Select. Active-low SPI Slave Select                                               | _                      | _                 |

| I2C_AD1/<br>SP[SCLK  | D4                                                                                                                | VA              | I                 | input.<br>I <sup>2</sup> C Slave Device Address Select 1. Used with I2C_AD0,<br>connected to VA or GNDA, to select between four possible<br>addresses.                                                                                                   | _                      | _                 |

|                      |                                                                                                                   |                 |                   | SPI Control-Port Clock. SPI clock input.                                                                                                                                                                                                                 |                        |                   |

| I2C_SCL/<br>SPI_MISO | E5                                                                                                                | VA              | I/O               | I <sup>2</sup> C Control-Port Clock. Clock input for the I <sup>2</sup> C interface.<br>SPI Control-Port Master In Slave Out. SPI data output.                                                                                                           | —                      | Hi-Z              |

| I2C_SDA/<br>SPI_MOSI | E3                                                                                                                | VA              | I/O               | I <sup>2</sup> C Control-Port Data. Data input/output for the I <sup>2</sup> C interface.<br>SPI Control-Port Master Out Slave In. SPI data input.                                                                                                       | —                      | Hi-Z              |

| INT/GPIO2            | F4                                                                                                                | VA              | I/O               | Interrupt. Configurable as an open-drain or CMOS (push-pull),<br>programmable interrupt output.<br>General Purpose Input/Output Pin. Programmable GPIO with<br>alternate functions for MCLK input.                                                       | _                      | Hi-Z              |

| LDO_FILT+            | D5                                                                                                                | VA              | 0                 | <b>Digital Core LDO Output.</b> Decoupling point for the integrated LDO providing power to the digital core circuitry on the CS35L42.                                                                                                                    |                        | _                 |

| OUT+                 | D2                                                                                                                | VSPK            | 0                 | Differential Audio Output. Internal Class D amplifier output.                                                                                                                                                                                            |                        | _                 |

| OUT-                 | C2                                                                                                                | VSPK            | 0                 | Differential Audio Output. Internal Class D amplifier output.                                                                                                                                                                                            | _                      |                   |

| RESET                | E2                                                                                                                | VA              | I                 | <b>Reset.</b> If this pin is driven low, the device enters a low power mode, all outputs are set to Hi-Z, all register values are set to their default settings and all DSP volatile memories (RAM) are invalidated.                                     | _                      | _                 |

| SW                   | A2, B2                                                                                                            | VBST            | l                 | <b>Boost Switch.</b> Input to internal boost FETs. Connect to $L_{BST}$ inductor.                                                                                                                                                                        | _                      |                   |

| SYNC/GPI01           | F3                                                                                                                | VA              | I/O               | Multidevice Synchronization Data. Serial data bus for<br>communicating operational state information across devices in<br>multi-channel applications.<br>General Purpose Input/Output Pin. Programmable GPIO with<br>alternate functions for MCLK input. | _                      | Hi-Z              |

| VA                   | F5                                                                                                                |                 | I                 | Analog Power. Power supply for internal analog and digital sections.                                                                                                                                                                                     |                        | _                 |

| VBST                 | A1, B1                                                                                                            | _               | 0                 | Boosted Supply from Boost Converter. Internal boost converter output.                                                                                                                                                                                    | _                      | _                 |

| Pin Name Ball # Power I/O Description |        | Description | Internal<br>Connection | State at<br>Reset                                                                                         |   |   |

|---------------------------------------|--------|-------------|------------------------|-----------------------------------------------------------------------------------------------------------|---|---|

| VP                                    | A5     | _           | I                      | <b>Boost Converter Power.</b> Power supply for the boost converter and portions of the Class D amplifier. | _ | _ |

| VSNS+                                 | F1     | VSPK        | Ι                      | <b>Voltage Sense Input.</b> Sense voltage for signal originating from OUT+.                               | — |   |

| VSNS-                                 | E1     | VSPK        | Ι                      | <b>Voltage Sense Input.</b> Sense voltage for signal originating from OUT                                 | _ | — |

| VSPK                                  | C1, D1 |             | Ι                      | <b>Amplifier Power.</b> Power supply for the Class D amplifier's output stage.                            | — |   |

#### Table 1-1. WLCSP Pin Descriptions (Cont.)

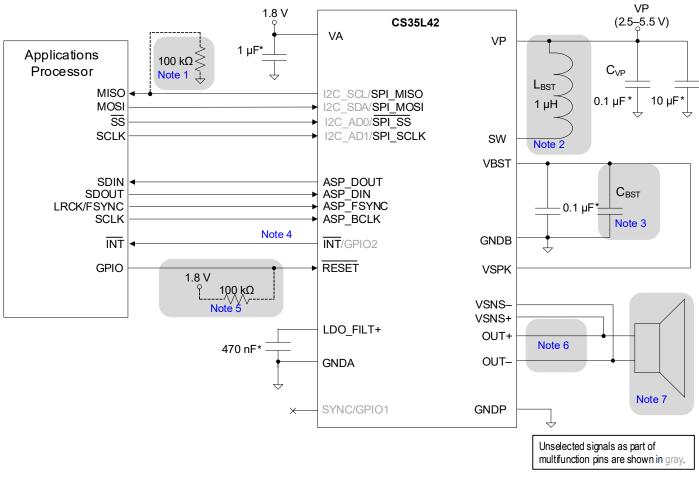

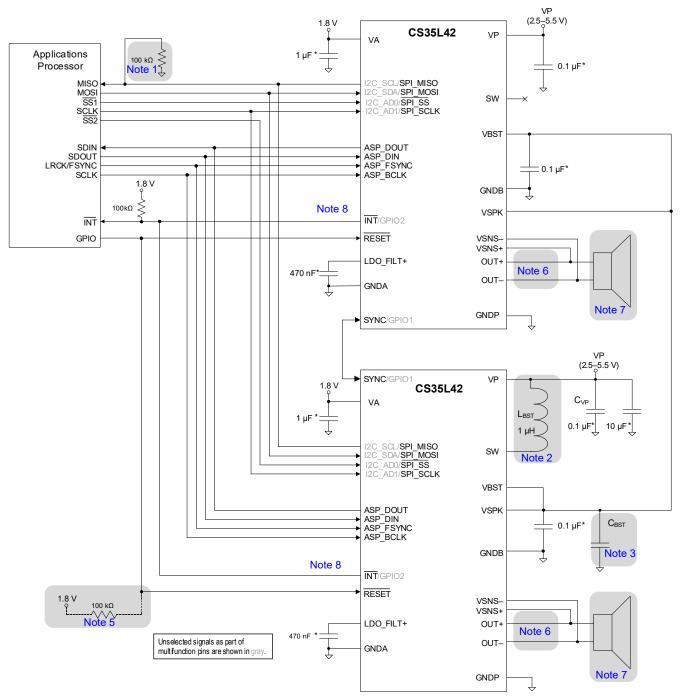

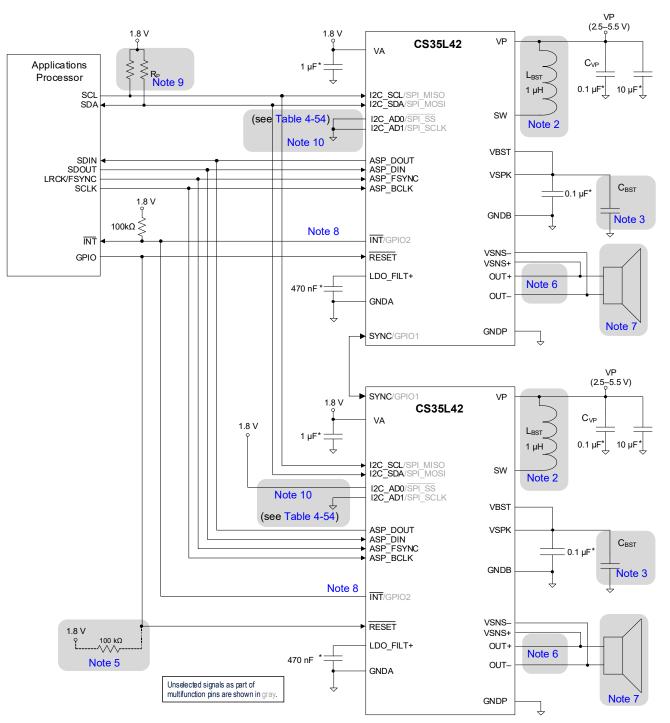

## 2 Typical Connection Diagrams

Figure 2-1. Typical Connection Diagram—Mono Configuration (Internal Boost Converter) and SPI Control

Figure 2-2. Typical Connection Diagram—Stereo Configuration with Shared Boost and SPI Control

Figure 2-3. Typical Connection Diagram—Stereo Configuration with Separate Boost and I<sup>2</sup>C Control

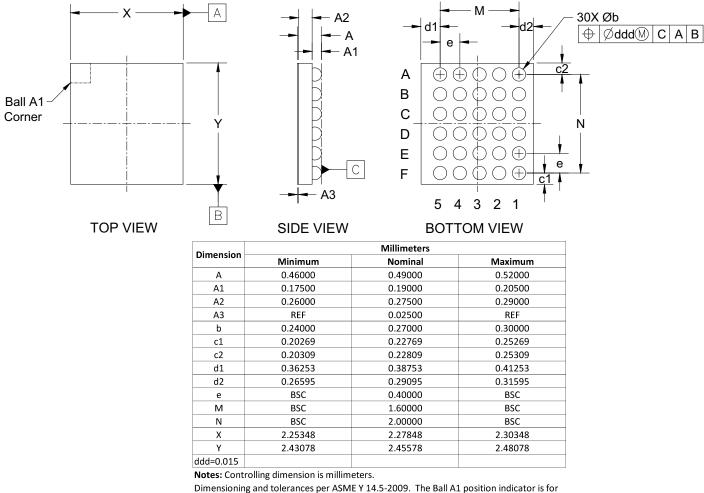

## 3 Package Dimensions

### 3.1 WLCSP Package Dimensions

Dimensioning and tolerances per ASME Y 14.5-2009. The Ball A1 position indicator is for illustration purposes only. Dimension "b" applies to the solder sphere diameter and is measured at the maximum solder sphere diameter, parallel to primary Datum C. X/Y Tolerances can apply to an individual edge increasing or decreasing by 25um.

Figure 3-1. WLCSP Package Dimensions

### 4 Package Marking

#### Top Side Brand

Line 1: Customer-designated part number Line 2: Package mark Line 3: Country of origin Line 4: Encoded Wafer/Device ID

RR = Device revision code LL = Lot sequence code YY = Year of manufacture WW = Work week of manufacture

Figure 4-1. Package Marking

# **5** Ordering Information

#### Table 5-1. Ordering Information

| Product | Description                                        | Package          | RoHS<br>Compliant | Grade      | Temperature<br>Range | Container     | I/O<br>Option | Order Number |

|---------|----------------------------------------------------|------------------|-------------------|------------|----------------------|---------------|---------------|--------------|

| CS35L42 | 11 V Boosted Mono<br>Class D Amplifier with<br>DSP | 30-ball<br>WLCSP | Yes               | Commercial | -40°C to +85°C       | Tape and Reel | 1.8 V         | CS35L42-CWZR |

#### **Contacting Cirrus Logic Support**

For all product questions and inquiries, contact a Cirrus Logic Sales Representative.

To find one nearest you, go to www.cirrus.com.

#### IMPORTANT NOTICE

The products and services of Cirrus Logic International (UK) Limited; Cirrus Logic, Inc.; and other companies in the Cirrus Logic group (collectively either "Cirrus Logic" or "Cirrus") are sold subject to Cirrus Logic's terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. Software is provided pursuant to applicable license terms. Cirrus Logic reserves the right to make changes to its products and specifications or to discontinue any product or service without notice. Customers should therefore obtain the latest version of relevant information from Cirrus Logic to verify that the information is current and complete. Testing and other quality control techniques are utilized to the extent Cirrus Logic deems necessary. Specific testing of all parameters of each device is not necessarily performed. In order to minimize risks associated with customer applications, the customer must use adequate design and operating safeguards to minimize inherent or procedural hazards. Cirrus Logic is not liable for applications assistance or customer product design. The customer is solely responsible for its overall product design, end-use applications, and system security, including the specific manner in which it uses Cirrus Logic components. Certain uses or product designs may require an intellectual property license from a third party. Features and operations described herein are for illustrative purposes only and do not constitute a suggestion or instruction to adopt a particular product design or a particular product design o

CIRRUS LOGIC PRODUCTS ARE NOT DESIGNED, TESTED, INTENDED OR WARRANTED FOR USE (1) WITH OR IN IMPLANTABLE PRODUCTS OR FDA/ MHRA CLASS III (OR EQUIVALENT CLASSIFICATION) MEDICAL DEVICES, OR (2) IN ANY PRODUCTS, APPLICATIONS OR SYSTEMS, INCLUDING WITHOUT LIMITATION LIFE-CRITICAL MEDICAL EQUIPMENT OR SAFETY OR SECURITY EQUIPMENT, WHERE MALFUNCTION OF THE PRODUCT COULD CAUSE PERSONAL INJURY, DEATH, SEVERE PROPERTY DAMAGE OR SEVERE ENVIRONMENTAL HARM. INCLUSION OF CIRRUS LOGIC PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK AND CIRRUS LOGIC DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS LOGIC PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS LOGIC PRODUCTS IN SUCH A MANNER, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS LOGIC, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

This document is the property of Cirrus Logic, and you may not use this document in connection with any legal analysis concerning Cirrus Logic products described herein. No license to any technology or intellectual property right of Cirrus Logic or any third party is granted herein, including but not limited to any patent right, copyright, mask work right, or other intellectual property rights. Any provision or publication of any third party's products or services does not constitute Cirrus Logic's approval, license, warranty or endorsement thereof. Cirrus Logic gives consent for copies to be made of the information contained herein only for use within your organization with respect to Cirrus Logic integrated circuits or other products of Cirrus Logic, and only if the reproduction is without alteration and is accompanied by all associated copyright, proprietary and other notices and conditions (including this notice). This document and its information is provided "AS IS" without warranty of any kind (express or implied). All statutory warranties and conditions are excluded to the fullest extent possible. No responsibility is assumed by Cirrus Logic for the use of information herein, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. Cirrus Logic, Cirrus, the Cirrus Logic logo design, and SoundClear are among the trademarks of Cirrus Logic. Other brand and product names may be trademarks or service marks of their respective owners.

Copyright © 2025 Cirrus Logic, Inc. and Cirrus Logic International Semiconductor Ltd. All rights reserved.